[解決済み] Verilog エラー。構造ネット式に接続する必要があります

2022-02-28 08:46:03

質問

エラーが発生するのですが。

output or inout port "Qout" must be connected to a structural net expression

. 以下のコードでエラーが発生した行をコメントアウトしています(コードはトリミング/圧縮されています)。Qをwireにすれば解決すると思うのですが、Qは8BitRegisterモジュールのalways-blockの一部なので、regでなければなりません。 どうすればこのエラーを回避できるでしょうか?

`timescale 1ns / 1ns

module lab4_3(SW, KEY, LEDR);

input [9:0] SW;

input [3:0] KEY;

output [7:0] LEDR;

eightBitRegister eight1(

.DATA_IN(SW[7:0]),

.parallelloadn(KEY[1]),

.rotateRight(KEY[2]),

.clock(KEY[0]),

.reset(SW[9]),

.Q(LEDR[7:0])

);

endmodule

module eightBitRegister(DATA_IN, parallelloadn, rotateRight, reset, clock, Q);

input [7:0] DATA_IN;

input parallelloadn;

input rotateRight;

input reset;

input clock;

output[7:0] Q;

register reg0(.Qout(Q[0]), //GETTING ERROR HERE

.right(Q[1]),

.left(Q[7]),

.D(DATA_IN[0]),

.loadleft(rotateRight),

.loadn(parallelloadn),

.clk(clock),

.rst(reset));

reg [7:0] Q;

always @(*)

begin

case({parallelloadn,rotateRight})

2'b00: Q = DATA_IN;

2'b01: Q = DATA_IN;

2'b11: Q = Q >> 1;

2'b10: Q = Q << 1;

endcase

end

endmodule

module register(Qout, right, left, D, loadleft, loadn, clk, rst);

input right, left;

input D;

wire datato_dff, rotatedata;

input loadleft, loadn;

input clk, rst;

output Qout;

flipflop F0(

.d(datato_dff),

.q(Qout),

.clock(clk),

.reset(rst)

);

module flipflop(d, q, reset, clock);

input reset, clock;

input d;

output q;

reg q;

always @(posedge clock)

begin

if (reset == 1'b0)

q <= 0;

else

q <= d;

end

endmodule

解決方法は?

まず最初に

endmodule

の後にある

flipflop F0

のインスタンス化です。Verilog では、ネストされたモジュールはサポートされていません(タイポエラーの可能性があります)。

次に

Qout

は複数のドライバで駆動します。あなたが駆動している

Qout

から

.Qout(Q[0])

レジスタモジュールから、そして

always

ブロックに格納されます。これは違法です。

モジュールの出力は、必ず

wire

. しかし

Qout

は出力ポートですが、ロジックの入力として使用されます。

Q

. そこで

register

モジュールを駆動するために使用します。

Q

の

eightBitRegister

モジュールになります。

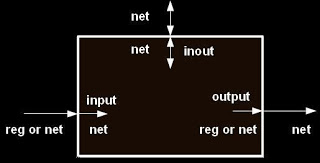

以下の図は、入力ポート、出力ポート、および入力ポートに対するポート接続ルールを示しています。

あなたのコードを少し修正しました。ここでは、一時的なワイヤーを使用して回避しています。このコードは、次の場所で入手できます。 EDAPlayground .

関連

最新

-

nginxです。[emerg] 0.0.0.0:80 への bind() に失敗しました (98: アドレスは既に使用中です)

-

htmlページでギリシャ文字を使うには

-

ピュアhtml+cssでの要素読み込み効果

-

純粋なhtml + cssで五輪を実現するサンプルコード

-

ナビゲーションバー・ドロップダウンメニューのHTML+CSSサンプルコード

-

タイピング効果を実現するピュアhtml+css

-

htmlの選択ボックスのプレースホルダー作成に関する質問

-

html css3 伸縮しない 画像表示効果

-

トップナビゲーションバーメニュー作成用HTML+CSS

-

html+css 実装 サイバーパンク風ボタン